This is the project I did during my internship at Cadence Design System. As you can tell from the name of the project and the place where I dit it, you can tell it’s a project that trying to apply the DNN techniques which got lots of attentions in both the academy and industry to the classical electronic design automation (EDA) area.

Routing Congestion

Routing congestion happens mostly when routing needs can’t be met with the available routing resources. This mostly results from congested placement that place too many standard cells or macros into . Although it may appear in certain academic literature, iterative physicial design method (redo placement if routing failed because of routing congestion) is unacceptable in commercial software. There should be a way to predict routing congestion in the placement phase to help the placement. Existing methods to predict routing congestion at placement stage mainly perform a simplified version of routing to model the actual routing and see if routing resources are enough. The problem of these methods are typically low accuracy and/or high computation demands. Data-driven method is in pursuit for better accuracy and lower computation needs.

Data-driven routing congestion prediction

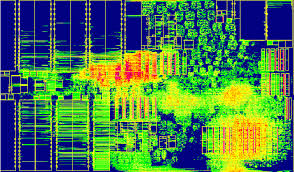

In the project, I approached the problem of routing congestion prediction through the data-driven method considering that an EDA company like Cadence has considerable amount of design examples to support the training of the data driven method. In the placement phase, we would be able to calculate the routing needs going in and out a local area, which is normally called cell. This is the unit of the glocal placement problem (For those who are not familiar, placement problem are often approached with divide and conquer: First, the whole chip area are divided into many small placement cells first. Second, perform global placement where the standard cells are assigned to different placement cells. Third, in each placement cell, detailed placement would determine how each standard cell would layout.). In the meantime we could also estimate the routing resources available in each placement cell. For a circuit design, the data of routing resources and routing demands of each global placement cell available at the placement stage can be viewed as a two-chanel image. And we would perform actual routing to get the labels, i.e. the severity of routing congestion in each placement cell. I utilized a simplified version of AlexNet as the neural network architecture. The trained model achieve over eighty percent of accuracy on predicting ten discrete levels of routing congestion. And it reduce the computation needs since congestion prediction is only a O(N) inference on the trained neural net rather than a O(N^2) pre routing.